La plupart des spécifications clés sont décrites

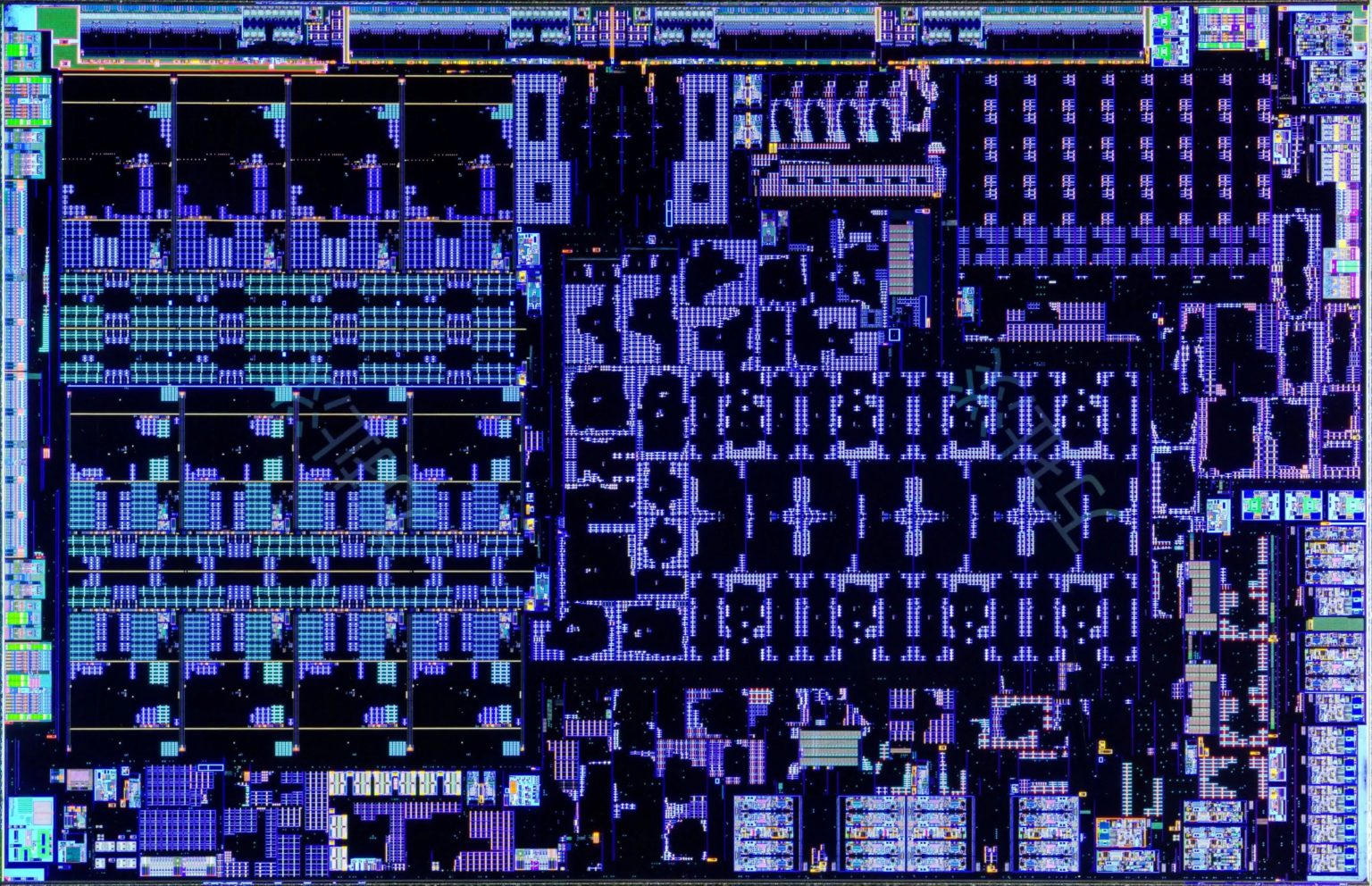

Qu'est-ce qui vient de se passer? Team Red fait feu de tout bois avec ses derniers processeurs mobiles « Strix Point » lancés cet été, représentant une mise à niveau générationnelle par rapport aux puces Phoenix de l'année dernière. De nouvelles images sont sorties, et le changement le plus évident est l'augmentation de la taille de la puce de 9,06 mm x 15,01 mm sur Phoenix à 12,06 mm x 18,71 mm, ce qui permet de sérieuses mises à niveau sous le capot.

Au cœur de ce processeur se trouve une conception hybride de processeur x86 avec deux clusters : l'un est doté de quatre cœurs Zen 5 puissants et de 16 Mo de cache L3, tandis que l'autre est doté de huit cœurs Zen 5c axés sur l'efficacité, chacun avec 8 Mo de cache L3. Les clusters communiquent via l'interconnexion Infinity Fabric d'AMD.

Mais la véritable star du spectacle est le GPU RDNA 3.5 intégré. Cette unité comprend 16 unités de calcul se traduisant par 1 024 processeurs de flux, plus quatre backends de rendu et 2 Mo de cache L2 pour alimenter cette bête en données. AMD avait déjà partagé quelques benchmarks officiels pour l'architecture, montrant qu'il s'agissait de bien plus qu'une simple mise à jour de mi-cycle par rapport au RDNA 3 de l'année dernière.

image de rendu pic.twitter.com/mqPg7YngOi

– í¬ìÂÂí¬ì (@harukaze5719) 29 juillet 2024

Le multimédia est également un domaine d'intérêt, avec des moteurs multimédia et d'affichage dédiés qui accélèrent l'encodage/décodage vidéo et la sortie d'affichage. Le moteur multimédia gère les derniers codecs comme AV1, H.264 et H.265. Le moteur d'affichage compresse et encode les images rendues par le GPU pour une sortie transparente via DisplayPort, HDMI et les connexions d'affichage intégrées. Ces blocs matériels optimisent Strix Point pour une lecture vidéo et une création de contenu fluides.

Ensuite, il y a le moteur d'IA de deuxième génération d'AMD, basé sur l'architecture XDNA 2 et doté de 32 tuiles avec un débit de 50 TOPS. Il s'agit en fait du troisième composant logique principal de la puce et il est visiblement plus grand que son homologue Phoenix. Ce NPU est conçu pour suivre les charges de travail d'IA avancées comme l'assistant Copilot+ de Microsoft.

Annoté ! ðÂÂÂ

C'est drôle de voir comment les unités scalaires RDNA WGP continuent d'être déplacées, revenons maintenant à la disposition RDNA1.

La SRAM autour de l'IMC est également présente sur PHX2 (et vraisemblablement PHX1), mais apparemment pas sur l'IOD de bureau ou les anciens CPU/APU.

Globalement… propre, sans surprises majeures. https://t.co/cf6MZVMgT2 pic.twitter.com/MfPqQRDGcY

– Nemez (@GPUsAreMagic) 29 juillet 2024

La prise en charge de la mémoire est également améliorée avec un contrôleur DDR5/LPDDR5 à double canal fonctionnant à des vitesses élevées, ainsi qu'un cache SRAM intégré similaire aux conceptions AMD précédentes. Le complexe racine PCIe a été réduit à 16 voies au lieu de 20 sur Phoenix.

Sous le capot, AMD a adopté la technologie de processus N4P de TSMC, une version améliorée du N4 utilisé dans l'itération précédente. Cela permet d'obtenir des horloges plus élevées et une meilleure efficacité énergétique.

Dans l'ensemble, Strix Point s'annonce comme une mise à niveau massive. Le GPU intégré devrait notamment permettre de jouer en 1080p sans GPU distinct.