L’écosystème du nouveau processus est presque prêt, avec quelques éléments manquants ici et là

Prospectif : TSMC poursuit les préparatifs pour ses technologies de processus de fabrication de classe 2 nm. Le matériel progresse bien, tandis que les sociétés tierces et les concepteurs de puces devront s’adapter à la multitude d’innovations proposées par N2.

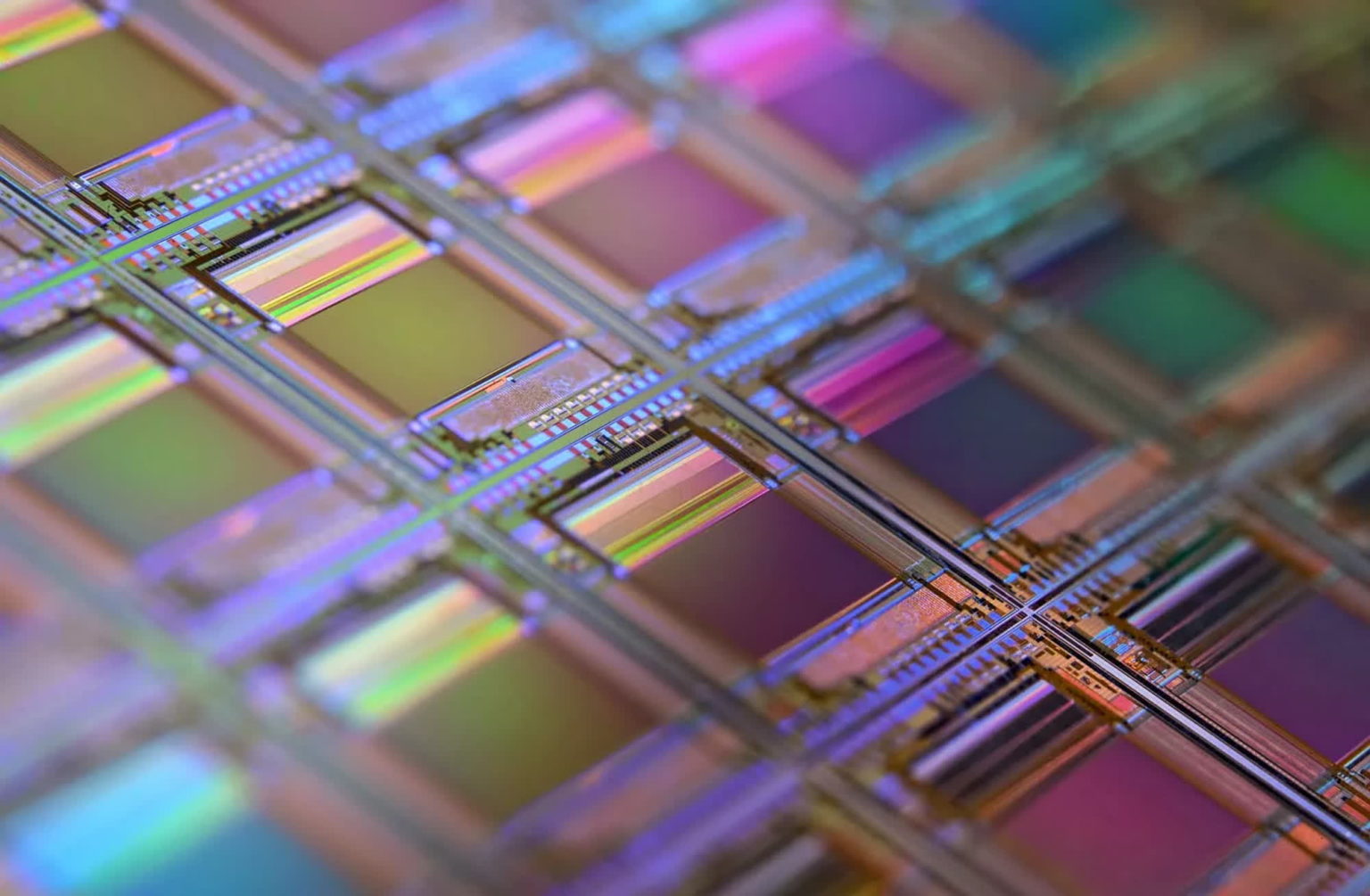

Au cours des prochaines années, la fonderie taïwanaise TSMC introduira certaines des technologies de fabrication de puces les plus avancées de la planète. Les technologies de traitement N2, N2P et N2X basées sur 2 nanomètres comprendront de multiples innovations, et l’ensemble de l’écosystème en orbite autour de l’activité silicium de l’entreprise est destiné à évoluer en conséquence.

Comme l’a noté AnandTech, N2 et ses futures itérations devraient apporter de nombreuses améliorations aux micropuces, notamment une réduction de la consommation électrique (-25-30%), plus de performances (+10-15%) et une densité de transistors (>1,15x). dans une configuration de puce « mixte » (50% logique, 30% SRAM, 20% analogique). La fabrication en série de puces 2 nm devrait arriver au second semestre 2025, mais TSMC travaille avec ses clients et partenaires 2 ans à l’avance car la « nanofeuille est différente ».

Le processus N2 comprendra des innovations telles que des transistors à grille tout autour (GAA), une alimentation électrique arrière et des condensateurs métal-isolant-métal de très haute performance (SHPMIM). TSMC a déclaré lors de son dernier forum sur la plateforme d’innovation ouverte en Europe que pour tirer parti de ces nouvelles technologies, les principaux concepteurs de puces doivent utiliser de nouveaux outils de simulation, de vérification et d’IP d’automatisation de la conception électronique (EDA).

Les transistors GAA se comportent différemment des transistors FinFET, a prévenu TSMC. Par conséquent, les fabricants de puces devront démarrer leurs charges de travail de conception essentiellement à partir de zéro. Développer de nouvelles adresses IP basées sur la mise à niveau du processus 2 nm n’est pas « plus difficile », a déclaré TSMC, c’est juste différent. Les entreprises devront s’adapter à la nouvelle technologie, tout comme elles sont passées des transistors planaires à une conception « 3D » (FinFET) dans le passé.

Les principaux fabricants de logiciels EDA (Cadence, Synopsys) ont déjà été certifiés par TSMC pour travailler sur N2, et les développeurs de puces peuvent immédiatement commencer à utiliser les nouveaux outils. La partie la plus complexe de la transition 2 nm implique des conceptions de puces IP pré-construites, car TSMC est encore en train de construire certains blocs à inclure dans les conceptions susmentionnées.

Les éléments standards tels que GPIO/ESD, PLL, SRAM et ROM sont prêts à la fois pour les applications mobiles et de calcul haute performance (HPC). Certains composants existent sous la forme de kits de développement pré-silicium, tandis que d’autres ont déjà été testés sur du matériel réel. D’autres blocs N2 tels que la mémoire non volatile, l’IP d’interface et l’IP de chiplet ne sont pas encore disponibles, ce qui pourrait gêner les efforts de conception de puces. Des sociétés tierces telles qu’Alphawave, Cadence, Credo et eMemory y travaillent déjà, a déclaré TSMC.