Doubler la bande passante pourrait signifier doubler les performances

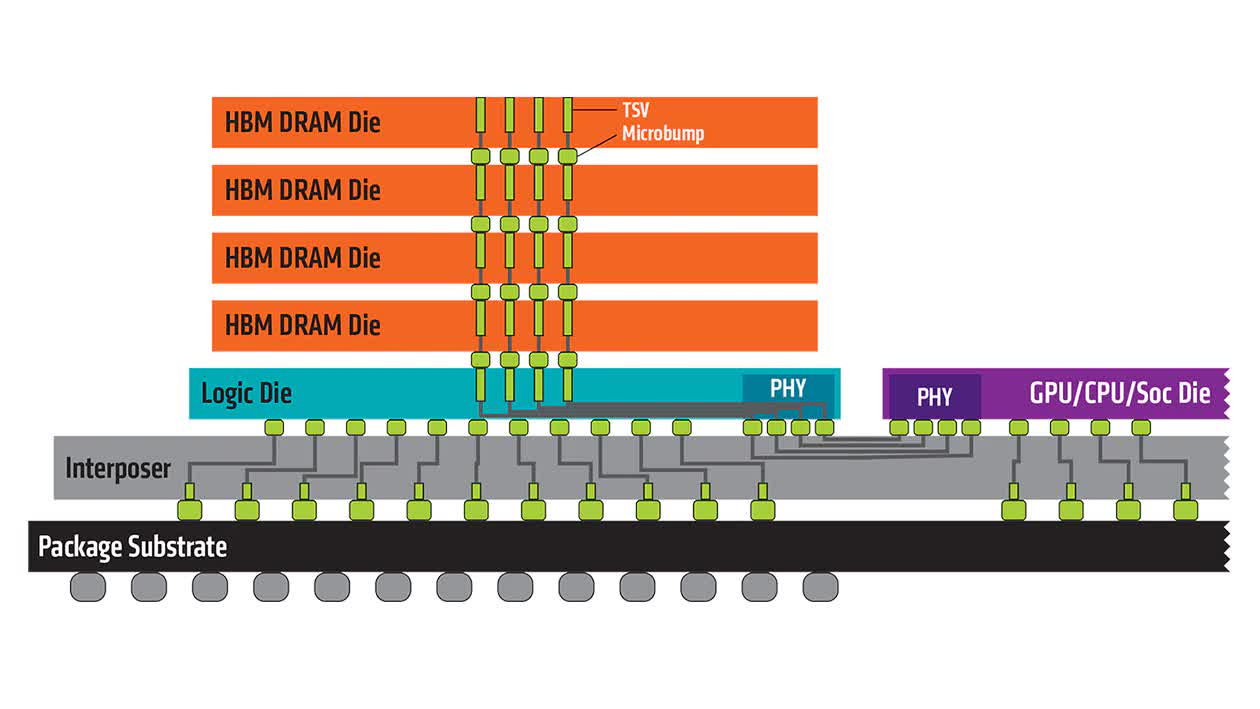

Dans le contexte: La première itération de mémoire à large bande passante (HBM) était quelque peu limitée, n’autorisant que des vitesses allant jusqu’à 128 Go/s par pile. Cependant, il y avait une mise en garde majeure : les cartes graphiques utilisant le HBM1 avaient une limite de 4 Go de mémoire en raison de limitations physiques.

Au fil du temps, les fabricants de HBM tels que SK Hynix et Samsung ont amélioré les défauts de HBM. La première mise à jour, HBM2, a doublé les vitesses potentielles à 256 Go/s par pile et les capacités maximales à 8 Go. En 2018, HBM2 a reçu une mise à jour mineure (HBM2E), qui a encore augmenté les limites de capacité à 24 Go et a apporté une nouvelle augmentation de vitesse, atteignant finalement 460 Go/s par puce à son apogée.

Lors du déploiement de HBM3, la vitesse a encore doublé, permettant un maximum de 819 Go/s par pile. Plus impressionnant encore, les capacités ont presque triplé, passant de 24 Go à 64 Go. Comme le HBM2E, le HBM3 a connu une autre mise à niveau à mi-vie, le HBM3E, qui a augmenté les vitesses théoriques jusqu’à 1,2 To/s par pile.

En cours de route, HBM a été progressivement remplacé dans les cartes graphiques grand public par une mémoire GDDR plus abordable. La mémoire à large bande passante est devenue une norme dans les centres de données, les fabricants de cartes destinées au lieu de travail choisissant d’utiliser une interface beaucoup plus rapide.

Tout au long des différentes mises à jour et améliorations, HBM a conservé la même interface de 1 024 bits (par pile) dans toutes ses itérations. Selon un rapport coréen, cela pourrait enfin changer lorsque le HBM4 arrivera sur le marché. Si les affirmations sont valables, l’interface mémoire doublera, passant de 1 024 bits à 2 048 bits.

Passer à une interface 2 048 pourrait théoriquement doubler à nouveau les vitesses de transfert. Malheureusement, les fabricants de mémoire pourraient ne pas être en mesure de maintenir les mêmes taux de transfert avec le HBM4 qu’avec le HBM3E. Cependant, une interface mémoire plus élevée permettrait aux fabricants d’utiliser moins de piles dans une carte.

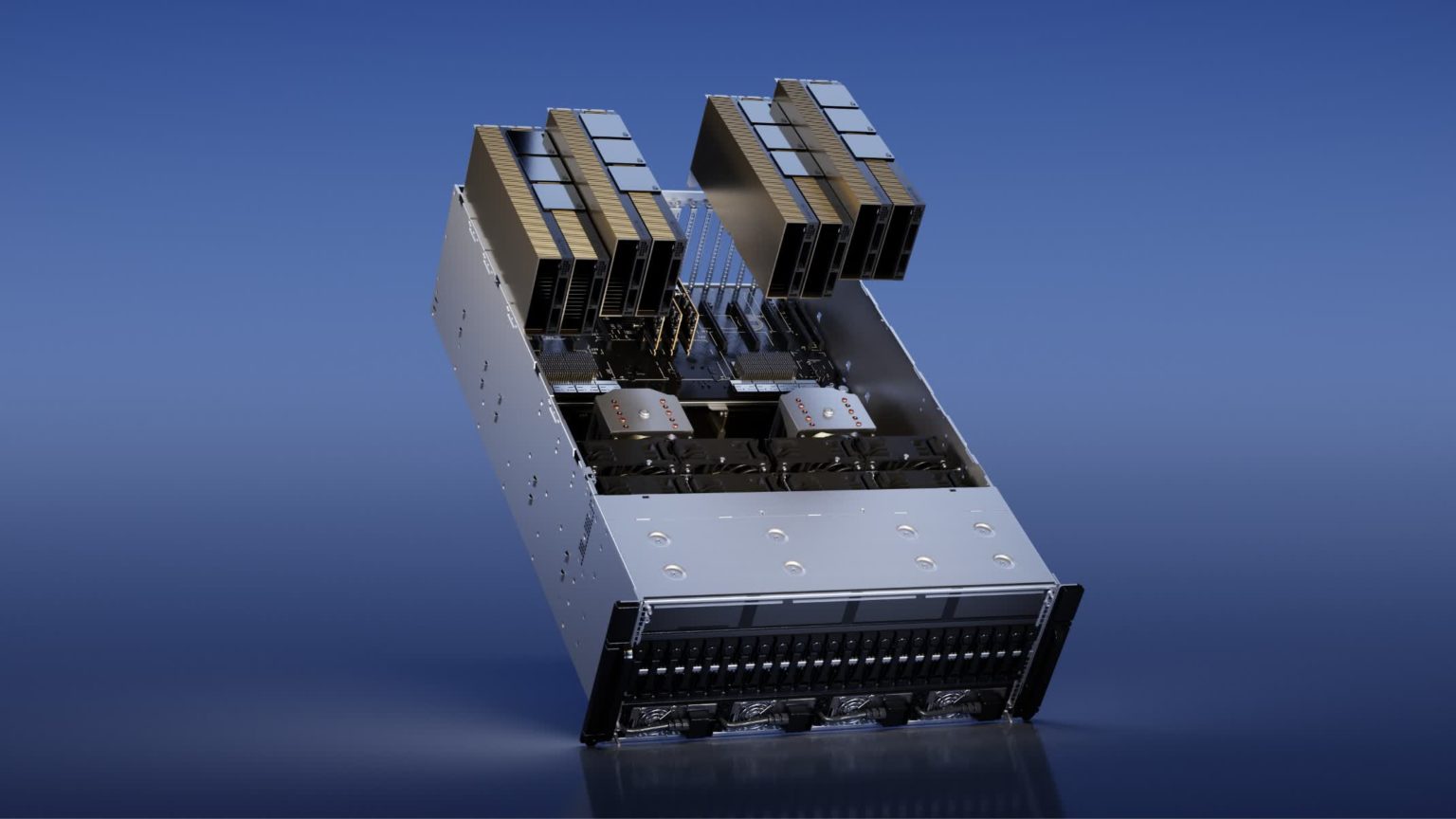

Par exemple, la carte IA phare de Nvidia, la H100, utilise actuellement six puces empilées de 1 024 bits, ce qui permet une interface de 6 144 bits. Si l’interface mémoire doublait à 2 048 bits, Nvidia pourrait théoriquement réduire de moitié le nombre de puces à trois et bénéficier des mêmes performances. Bien sûr, on ne sait pas exactement quelle voie les fabricants emprunteront, car le HBM4 sera presque certainement en production dans des années.

Actuellement, SK Hynix et Samsung pensent pouvoir atteindre un « rendement de 100 % » avec le HBM4 lorsqu’ils commenceront à le fabriquer. Seul le temps nous dira si les rapports tiennent la route, alors prenez les nouvelles avec des pincettes.