Un microcontrôleur tolérant aux pannes conçu pour les vaisseaux spatiaux à énergie limitée

Prospectif : Très peu d’appareils électroniques utilisés ici sur Terre peuvent survivre lorsqu’ils quittent l’atmosphère confortable de la planète. Les processeurs, en particulier, doivent être conçus pour résister aux conditions difficiles de l’espace, notamment aux radiations et aux températures quasi nulles. Il semble que RISC-V pourrait aider à relever ce défi.

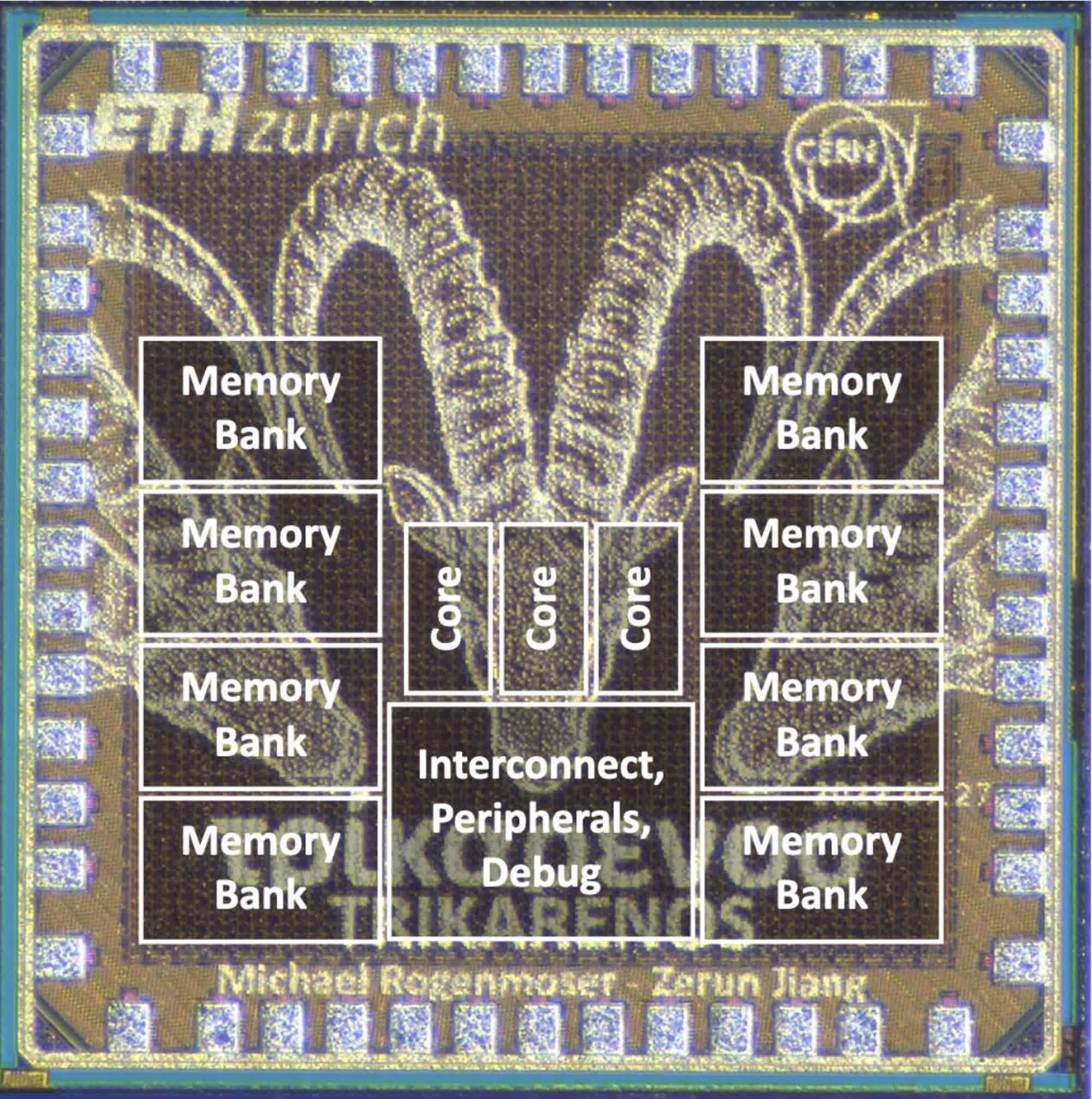

Des chercheurs de l’université publique suisse ETH Zurich ont développé Trikarenos, un microcontrôleur basé sur RISC-V conçu pour fonctionner de manière fiable dans des environnements difficiles comme l’espace. Les Trikarenos peuvent résister aux perturbations d’événement unique (SEU) induites par les radiations, qui sont des changements dans l’état d’un dispositif microélectronique provoqués par une seule particule ionisante. De plus, il peut offrir des niveaux de performances comparables aux « puces spatiales » traditionnelles tout en ne consommant qu’une fraction du même budget énergétique.

Les contre-mesures courantes aux conditions spatiales reposent généralement sur des technologies exclusives résistantes aux radiations, des nœuds de fabrication à faible densité et une réplication étendue, comme l’expliquent les chercheurs. Ces facteurs contribuent à des coûts élevés et à de faibles niveaux de performance et d’efficacité. Trikarenos vise à relever ces défis avec une architecture CPU RISC-V 32 bits et une technologie de fabrication « avancée » en 28 nm fournie par TSMC.

Le nœud de 28 nm a démontré sa résilience aux « effets néfastes » des événements SEU induits par les radiations, selon les chercheurs, et il offre des niveaux d’efficacité sans précédent par rapport aux conceptions précédentes. Trikarenos utilise l’architecture de microcontrôleur PULPissimo à très faible consommation, qui est open source, tout comme l’architecture CPU RISC-V.

La puce intègre trois cœurs de calcul Ibex basés sur RISC-V, chacun cadencé à des vitesses allant jusqu’à 270 MHz, et ils sont alimentés en données par huit banques SRAM, chacune avec 256 Ko de mémoire. Ces trois cœurs fonctionnent dans une configuration « triple-core lockstep », où chaque cœur effectue la même opération simultanément. Dans le cas d’un événement SEU corrompant l’un des cœurs, un vote similaire à celui décrit dans le rapport minoritaire déterminerait le résultat de l’opération correcte.

D’autres éléments architecturaux conçus pour améliorer la tolérance aux rayonnements comprennent une redondance intégrée, des banques de mémoire de correction d’erreurs et un « épurateur de mémoire » qui lit en permanence chaque adresse mémoire pour corriger toute erreur corrigible. De plus, les trois noyaux Ibex sont physiquement séparés par un espace de 20 micromètres autour de chaque noyau.

La conception à trois cœurs offre une tolérance aux pannes accrue mais peut avoir un impact sur les performances potentielles du contrôleur. Néanmoins, la conception semble capable de fournir des niveaux de performances comparables à la puce RAD750 basée sur PowerPC, utilisée depuis deux décennies et toujours utilisée par les grandes agences spatiales pour leurs missions les plus complexes, comme le télescope spatial James Webb. Dans les années à venir, la NASA a l’intention de remplacer le RAD750 par un processeur RISC-V hautes performances conçu par SiFive.

Comparé au RAD750, qui consomme cinq watts d’énergie, Trikarenos peut obtenir les mêmes résultats de calcul avec seulement 15,7 milliwatts, ce qui le rend avantageux pour les missions à consommation énergétique limitée comme les lancements de satellites CubeSat. Si une fiabilité extrême n’est pas requise, les trois cœurs peuvent fonctionner en parallèle, offrant 300 % des performances d’une conception à triple cœur.