TSMC pense que le N3P surpassera le 18A, mais Intel introduira d’abord le gate-all-around

Coups de feu tirés : Alors que les fabricants de semi-conducteurs consolident leurs processus 3 nm et intensifient la course vers le 2 nm, TSMC et Intel ont récemment échangé des discussions pour savoir quelle entreprise disposera du nœud supérieur au cours des prochaines années. Le fabricant taïwanais est confiant dans sa trajectoire actuelle, mais Intel vise à réaffirmer sa domination dans l’industrie des semi-conducteurs en passant au 2 nm avant tout le monde.

Le PDG d’Intel, Pat Gelsinger, a affirmé que son prochain nœud de processus 18A (essentiellement 1,8 nm) pourrait surpasser les puces 2 nm de TSMC malgré son lancement un an plus tôt. Ces commentaires contredisent les récentes affirmations du concurrent taïwanais. Gelsinger a fait ces remarques dans une interview avec Barrons.

Il n’est pas sûr qu’un nœud surpassera considérablement l’autre, mais il a parlé avec optimisme de la fenêtre de publication de l’entreprise. Le média a présenté la course entre Intel et TSMC dans le contexte des tentatives américaines de sécuriser les approvisionnements en semi-conducteurs dans un contexte de tensions avec la Chine. En tant que leader du marché, TSMC fournit le silicium 3 nm pour les processeurs Apple iPhone 15 et M3 Mac.

La société a affirmé qu’un prochain nœud optimisé de 3 nm appelé N3P atteindrait une zone de performances de puissance comparable au 18A d’Intel. Le géant taïwanais prévoit de mettre le N3P en production de masse au cours du second semestre 2024, à peu près en même temps que le 20A (2 nm) et le 18A.

De plus, TSMC est convaincu que son nœud N2 de 2 nm, prévu pour 2025, surpassera le N3P et le 18A. Suivant le modèle de processus inaugural 3 nm de la société, Apple pourrait obtenir les premiers résultats sur N2 et l’utiliser pour l’iPhone 17 Pro.

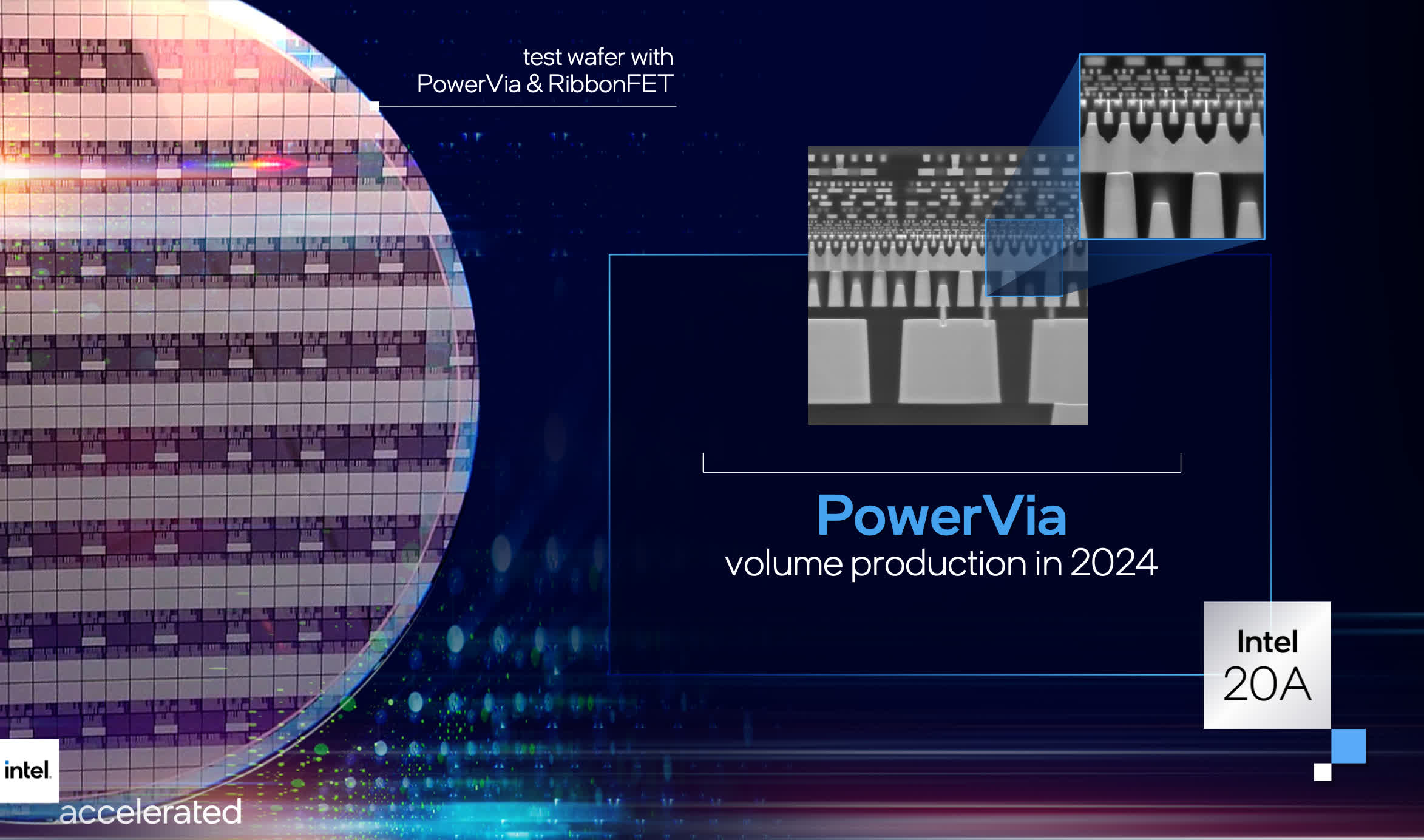

Une grande partie de la confiance de Gelsinger dans les transistors 20A et 18A réside dans l’introduction de l’architecture RibbonFET, la version de l’entreprise des transistors à grille complète (GAA) et de la fourniture de puissance à l’arrière. Ces technologies deviendront cruciales pour les entreprises fabriquant des puces de 2 nm, permettant des densités logiques et des vitesses d’horloge plus élevées avec une perte de puissance réduite. Pendant ce temps, le N3P de TSMC et d’autres nœuds 3 nm à venir continueront à utiliser l’architecture FinFET mature jusqu’à ce qu’ils migrent vers GAA avec N2 un an après Intel.

Intel et TSMC ne sont pas les seules entreprises à se préparer à construire des semi-conducteurs 2 nm. Samsung souhaite également se lancer dans la production de masse de 2 nm en 2025, tandis que le fabricant japonais Rapidus prévoit d’introduire des prototypes d’ici 2025, avec une production de masse débutant en 2027.