TSCM est très confiant quant à ses prochains processus de production de puces

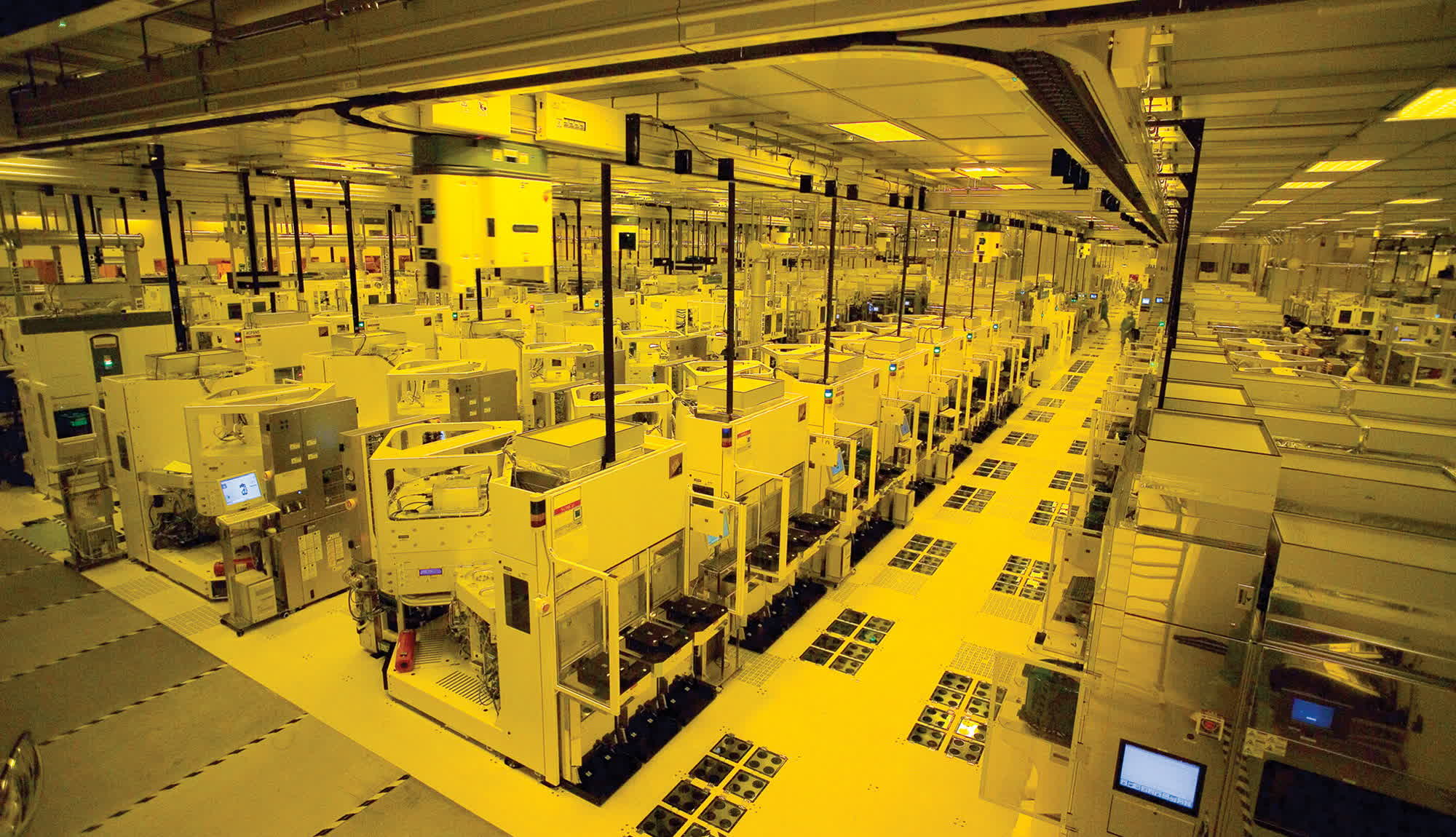

Pourquoi est-ce important: Au cours des prochaines années, l’industrie des puces électroniques connaîtra d’importantes avancées technologiques dans les processus de fabrication des composants en silicium. TSMC envisage l’avenir en toute confiance, affirmant que l’entreprise fournira des nœuds supérieurs à ceux développés par ses concurrents.

Les nœuds de processus futuristes 20A et 18A d’Intel devraient faire leurs débuts dans les nouveaux processeurs en 2024 ou 2025. Cependant, TSMC a déjà déclaré sa victoire sur la société américaine, avec l’intention d’introduire une technologie de fabrication comparable dans le même délai, mais avec des améliorations à tous les niveaux.

Lors d’une récente conférence téléphonique sur les résultats, CC Wei, PDG de TSMC, a déclaré que son évaluation interne confirmait les améliorations de la technologie N3P. Le nœud de fabrication de classe 3 nm de TSMC a démontré un « PPA comparable » (zone de performance énergétique) au nœud 18A d’Intel. N3P devrait être encore meilleur, en arrivant plus tôt sur le marché, en bénéficiant d’une « meilleure maturité technologique » et en offrant des avantages de coût significatifs.

Wei a souligné que TSMC ne sous-estime ni ne prend la concurrence à la légère. Il a également mentionné que la technologie 2 nanomètres de la société, bien qu’elle soit encore en cours de développement, devrait surpasser à la fois le N3P et le 18A. Le processus de fabrication de classe 2 nm de TSMC est en passe de devenir la technologie la plus avancée de l’industrie des semi-conducteurs lors de son introduction en 2025.

Intel devrait lancer les premiers processeurs fabriqués avec le processus 20A en 2024, apportant des innovations significatives à la technologie de fabrication de puces avec l’introduction de transistors à grille RibbonFET. RibbonFET représente la première refonte majeure des transistors depuis l’introduction des transistors FinFET en 2011 et intégrera une nouvelle technologie de réseau de distribution d’énergie arrière (BSPDN) connue sous le nom de PowerVia.

Dans le même temps, Wei a confirmé que TSMC continuera à utiliser la technologie éprouvée des transistors FinFET, ainsi que les méthodes traditionnelles de fourniture d’énergie, sur l’ensemble de sa gamme de processus 3 nm (N3, N3E, N3P, N3X). Les transistors à grille complète et le BSPDN seront introduits avec les nœuds N2, dont la production en grand volume est prévue au second semestre 2025.

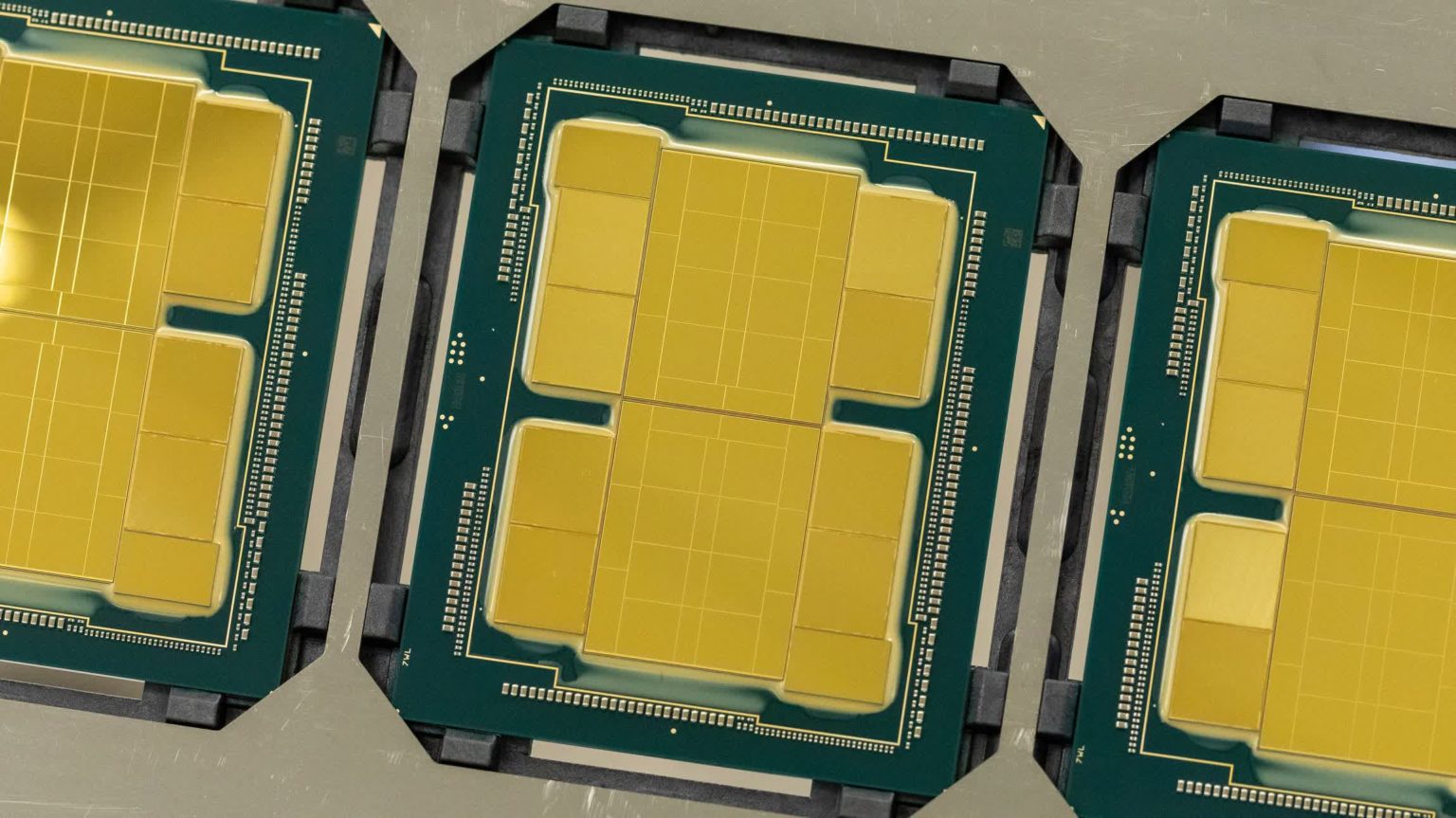

Wei a mentionné que N3 devrait contribuer à un « pourcentage moyen à un chiffre » du chiffre d’affaires total des plaquettes de TSMC en 2023, avec un pourcentage nettement plus élevé prévu pour 2024. Il existe une forte demande pour les produits 3 nm de la part de divers clients qui recherchent des performances améliorées. , l’efficacité énergétique, le rendement et la « prise en charge complète de la plate-forme » pour le calcul haute performance (HPC) et les applications pour smartphones.